표준공정

ISRC 0.25um CMOS 표준공정

산업자원부 지원으로 1,2차 반도체 연구기반 혁신사업을 통하여 6인치 0.3um 공정 라인을 구축하고,구축된 장비를 통하여 2008년 1월 6“ 0.25um CMOS (Double - Metal) 표준공정을 수립하였다.

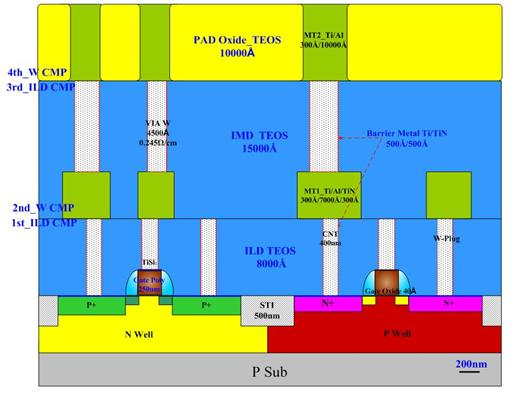

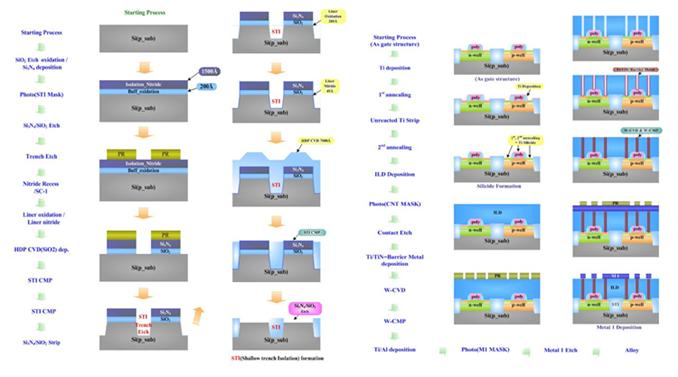

기존 0.5um CMOS공정과는 달리 소자의 성능 향상을 위하여 STI(Shallow Trench Isolation) 공정,TiSi2 공정, Barrier Metal / W-CVD, CMP 공정(W,ILD,IMD)에 대한 개발이 진행되었다.

저전압 회로 설계가 가능한 0.25㎛ CMOS 공정을 이용하여 우수한 chip을 제작할 수 있으리라 생각되며,관련기술을 산·학·연 연구자들에게 공유하여 다양한 기술 응용 및 적용이 이루어 질 것이라고 기대한다.

※ 0.25um CMOS Structure (2 Metal)

※ STI(Shallow Trench Isolation) Structure / TiSi2 , CMP & Barrier Metal Process

- 0.25㎛ CMOS 공정 관련 문의

- 지상엽 02)880-5458 syj@snu.ac.kr

이메일주소 무단 수집거부닫기

이를 위반 시 정보통신망법에 의해 형사 처벌됨을 유념하시기 바랍니다.

[게시일 2008년 2월 12일]

개인정보처리방침닫기

시행일자 2008. 2. 12.

최종수정일 2024. 5. 1.

서울대학교 반도체공동연구소 개인정보처리방침

안 내

서울대학교 반도체공동연구소(이하 “ISRC”이라 함)는 정보주체의 자유와 권리 보호를 위해 「개인정보 보호법」 및 관계 법령이 정한 바를 준수하여, 적법하게 개인정보를 처리하고 안전하게 관리하고 있습니다. 이에 「개인정보 보호법」 제30조에 따라 정보주체에게 개인정보 처리에 관한 절차 및 기준을 안내하고, 이와 관련한 고충을 신속하고 원활하게 처리할 수 있도록 하기위하여 다음과 같이 개인정보 처리방침을 수립·공개합니다. 또한 개정하는 경우 홈페이지를 통하여 공지할 것입니다. 이 방침은 별도의 설명이 없는 한 ISRC 홈페이지에 적용됨을 알려드립니다.

제1조 개인정보의 처리 목적

제1조 개인정보의 처리 목적

1. ISRC는 다음의 목적을 위하여 개인정보를 처리합니다. 처리하고 있는 개인정보는 다음의 목적 이외의 용도로는 이용되지 않으며, 이용 목적이 변경되는 경우에는 「개인정보 보호법」 제18조에 따라 별도의 동의를 받는 등 필요한 조치를 이행할 예정입니다.

① 서비스 제공

• ISRC의 소개 및 공지사항, 온라인서비스(입소신청, 공정접수 및 장비예약, 교육접수, 장비교육접수), 계정코드 생성, 본인인증, 증명서발급(교육 수료증) 등의 서비스 제공에 관련한 목적으로 개인정보를 처리합니다.

② 회원가입 및 관리

• ISRC에서 제공하는 온라인서비스(입소신청, 공정접수 및 장비예약, 교육접수, 장비교육접수) 등의 회원제 서비스 이용에 따른 본인확인, 개인식별, 부정이용 방지와 비인가 사용방지 등 민원처리, 공지사항, SMS, 이메일 전달 등의 목적으로 개인정보를 처리합니다.

제2조 개인정보의 처리 및 보유기간

제2조 개인정보의 처리 및 보유기간

1. ISRC는 법령에 따른 개인정보 보유·이용 기간 또는 정보주체로부터 개인정보를 수집 시 동의 받은 개인정보 보유·이용기간 내에서 개인정보를 처리합니다. 다만, 학칙이나 기타 법률에 의해 이용자의 개인정보를 보존해야할 필요가 있는 경우에는 해당 법률의 규정을 따릅니다.

2. ISRC에서 각종 서비스 제공을 위해 처리하는 개인정보의 항목, 수집방법, 보유기간은 다음과 같습니다.

① 홈페이지 회원 가입 및 관리

• 생년월일, 계정코드, 계정책임자, 성명(한글, 영문), 이메일, 소속, 직위/과정, 연락전화번호(휴대폰, 직장), 주요경력, 입소목적, 입소신청동의, 실명인증동의, SMS공지수신동의, 메일공지수신동의 등

② 인터넷 서비스 이용과정에서 아래 개인정보 항목이 자동으로 생성되어 수집될 수 있습니다. (자동으로 생성·수집되는 개인정보항목이 있는 경우)

• IP주소, 쿠키, MAC주소, 서비스 이용기록, 방문기록, 불량 이용기록

③ 보유기간

• 홈페이지 회원 가입 및 관리 : ISRC 홈페이지 탈퇴시까지 다만, 다음의 사유에 해당하는 경우에는 해당 사유 종료시까지

- 관계 법령 위반에 따른 수사·조사 등이 진행중인 경우에는 해당 수사, 조사 종료시까지

- 홈페이지 이용에 따른 채권, 채무관계 잔존시에는 해당 채권, 채무관계 정산시까지

3. 개인정보파일의 처리목적·보유기간 및 항목은 개인정보파일의 특성에 따라 달리 규정하고 있으며, 개인정보파일별 상세한 내용은 개인정보보호 종합포털을 통해 확인하시기 바랍니다.

※ 개인정보보호위원회 개인정보보호 포털(www.privacy.go.kr) → 민원마당 → 개인정보 열람등 요구 → 개인정보파일 목록검색에서 “서울대학교 반도체공동연구소”

제3조 개인정보의 제3자 제공에 관한 사항

제3조 개인정보의 제3자 제공에 관한 사항

1. ISRC 에서는 원칙적으로 이용자의 개인정보를 제1조 (개인정보의 처리 목적)에서 명시한 범위 내에서 처리하며, 이용자의 사전 동의 없이는 본래의 범위를 초과하여 처리하거나 제3자에게 제공하지 않습니다. 단, 다음의 경우에는 개인정보를 처리할 수 있습니다.

ISRC 에서는 원칙적으로 이용자의 개인정보를 제1조 (개인정보의 처리 목적)에서 명시한 범위 내에서 처리하며, 이용자의 사전 동의 없이는 본래의 범위를 초과하여 처리하거나 제3자에게 제공하지 않습니다. 단, 다음의 경우에는 개인정보를 처리할 수 있습니다.

① 이용자가 사전에 제3자 제공 및 공개에 동의한 경우

② 법률의 특별한 규정 등 「개인정보 보호법」 제17조 및 제18조에 의해 제공이 요구되는 경우

③ 서비스의 제공에 관한 계약의 이행을 위하여 필요한 개인정보로서 경제적/기술적인 사유로 통상의 동의를 받는 것이 현저히 곤란한 경우

④ 개인을 식별하기에 특정할 수 없는 상태로 가공하여 이용하는 경우

2. 국가나노인프라협의체 모아팹 연계에 의한 수집한 개인정보의 제3자 제공

① 반도체공동연구소는 국가나노인프라 팹서비스 통합정보시스템(이하 ‘모아팹(moafab.kr’)에서 이용자의 개인정보에 대하여 제3자 제공을 하고 있으며, 본인 확인의 목적으로 이메일 또는 휴대폰 및 I-PIN 인증시에 제공하는 개인정보는 개인정보보호법 제22조 제2항에 따라 정보주체와의 계약체결 등을 위하여 정보주체의 동의로 처리할 수 있는 개인정보로 지정합니다.

② 국가나노인프라 팹서비스 통합시스템 홈페이지 회원 서비스 제공을 위해 개인정보를 제공하는 기관 아래에 해당하는 개인정보는 정보주체의 동의 없이는 제공되지 않습니다.

- 개인정보파일명

- 피제공기관

- 제공항목

- 이용목적

- 보유기간

- 나노인프라 팹서비스 통합정보시스템 회원 정보

- 국가나노인프라협의체 소속 기관

- 이름,주소,연락처,전자우편,회원번호,신청이력 등

- 통합시스템 이용자에 대한 통합서비스 제공

- 회원탈퇴시까지

- 휴대폰인증 서비스

- NICE평가정보(주)

- 이름,휴대폰번호,내외국인구분

- 휴대폰 본인인증

- 목적범위 내 사용 후 폐기

- I-PIN 인증서비스

- NICE평가정보(주)

- 이름,내외국인구분

- I-PIN 본인인증

- 목적범위 내 사용 후 폐기

제4조 개인정보처리 위탁

제4조 개인정보처리 위탁

ISRC 에서는 원칙적으로 이용자의 동의 없이 해당 개인정보의 처리를 타인에게 위탁하지 않습니다.

제5조 개인정보의 파기절차 및 파기방법

제5조 개인정보의 파기절차 및 파기방법

1. ISRC에서는 개인정보 보유기간의 경과, 처리목적 달성 등 개인정보가 불필요하게 되었을 때에는 지체없이 해당 개인정보를 파기합니다.

2. 정보주체로부터 동의받은 개인정보 보유기간이 경과하거나 처리목적이 달성되었음에도 불구하고 다른 법령에 따라 개인정보를 계속 보존하여야 하는 경우에는, 해당 개인정보(또는 개인정보파일)를 별도의 데이터베이스(DB)로 옮기거나 보관장소를 달리하여 보존합니다.

① 파기절차

• 이용자가 입력한 정보는 목적 달성 후 별도의 DB에 옮겨져(종이의 경우 별도의 서류) 내부 방침 및 기타 관련 법령에 따라 일정기간 저장된 후 혹은 즉시 파기됩니다. 이 때, DB로 옮겨진 개인정보는 법률에 의한 경우가 아니고서는 다른 목적으로 이용되지 않습니다.

② 파기방법

• ISRC에서는 전자적 파일 형태로 기록·저장된 개인정보는 기록을 재생할 수 없도록 파기하며, 종이 문서에 기록·저장된 개인정보는 분쇄기로 분쇄하거나 소각하여 파기합니다.

제6조 정보주체와 법정대리인의 권리•의무 및 행사방법

제6조 정보주체와 법정대리인의 권리•의무 및 행사방법

1. 정보주체는 ISRC에 대해 언제든지 개인정보 열람·정정·삭제·처리정지 요구 등의 권리를 행사할 수 있습니다.

※ 만 14세 미만 아동에 관한 개인정보의 열람등 요구는 법정대리인이 직접 해야 하며, 만 14세 이상의 미성년자인 정보주체는 정보주체의 개인정보에 관하여 미성년자 본인이 권리를 행사하거나 법정대리인을 통하여 권리를 행사할 수도 있습니다.

2. 권리 행사는 ISRC에 대해 「개인정보 보호법」 시행령 제41조 제1항에 따라 서면, 전자우편, 모사전송(FAX) 등을 통하여 하실 수 있으며, ISRC은 이에 대해 지체없이 조치하겠습니다.

3. 권리 행사는 정보주체의 법정대리인이나 위임을 받은 자 등 대리인을 통하여 하실 수도 있습니다. 이 경우 “개인정보 처리 방법에 관한 고시(제2020-7호)” 별지 제11호 서식에 따른 위임장을 제출하셔야 합니다.

4. 개인정보 열람 및 처리정지 요구는 「개인정보 보호법」 제35조 제4항, 제37조 제2항에 의하여 정보주체의 권리가 제한 될 수 있습니다.

5. 개인정보의 정정 및 삭제 요구는 다른 법령에서 그 개인정보가 수집 대상으로 명시되어 있는 경우에는 그 삭제를 요구할 수 없습니다.

6. ISRC는 정보주체 권리에 따른 열람의 요구, 정정·삭제의 요구, 처리정지의 요구 시 열람 등 요구를 한 자가 본인이거나 정당한 대리인인지를 확인합니다.

제7조 개인정보의 안전성 확보 조치

제7조 개인정보의 안전성 확보 조치

ISRC는 개인정보의 안전성 확보를 위해 다음과 같은 조치를 취하고 있습니다.

1. 관리적 조치

① 개인정보 내부관리계획의 수립 및 시행 : 개인정보의 안전한 처리를 위하여 내부관리계획을 수립하여 시행하고 있습니다.

② 개인정보취급자 지정의 최소화 및 교육: 개인정보취급자의 지정을 최소화하고 정기적인 교육을 시행하고 있습니다.

개인정보 취급 관련 안정성 확보를 위해 정기적(반기 1회)으로 자체 감사를 실시하고 있습니다.

③ 정기적인 자체 감사 실시 : 개인정보 취급 관련 안정성 확보를 위해 정기적(반기 1회)으로 자체 감사를 실시하고 있습니다.

개인정보의 안전한 처리를 위하여 내부관리계획을 수립?시행하고 있습니다.

2. 기술적 조치

① 개인정보의 암호화 : 이용자의 개인정보 중 비밀번호, 생년월일은 암호화 되어 저장 및 관리되고 있어, 본인만이 알 수 있으며 중요한 데이터는 파일 및 전송 데이터를 암호화 하거나 파일 잠금 기능을 사용하는 등의 별도 보안기능을 사용하고 있습니다.

② 개인정보에 대한 접근 제한 : 개인정보를 처리하는 데이터베이스시스템에 대한 접근권한의 부여,변경,말소를 통하여 개인정보에 대한 접근통제를 위하여 필요한 조치를 하고 있으며 침입차단시스템을 이용하여 외부로부터의 무단 접근을 통제하고 있습니다.

ISRC 에서는 해킹이나 컴퓨터 바이러스 등에 의한 개인정보 유출 및 훼손을 막기 위하여 보안프로그램을 설치하고 주기적인 갱신·점검을 하며 외부로부터 접근이 통제된 구역에 시스템을 설치하고 기술적/물리적으로 감시 및 차단하고 있습니다.

③ 해킹 등에 대비한 기술적 대책 : 해킹이나 컴퓨터 바이러스 등에 의한 개인정보 유출 및 훼손을 막기 위하여 보안프로그램을 설치하고 주기적인 갱신·점검을 하며 외부로부터 접근이 통제된 구역에 시스템을 설치하고 기술적/물리적으로 감시 및 차단하고 있습니다.

개인정보를 처리하는 데이터베이스시스템에 대한 접근권한의 부여,변경,말소를 통하여 개인정보에 대한 접근통제를 위하여 필요한 조치를 하고 있으며 침입차단시스템을 이용하여 외부로부터의 무단 접근을 통제하고 있습니다.

3. 물리적 조치

① 비인가자에 대한 출입 통제 : 개인정보를 보관하고 있는 물리적 보관 장소를 별도로 두고 이에 대해 출입통제 절차를 수립, 운영하고 있습니다.

제8조 개인정보를 자동으로 수집하는 장치의 설치· 운영 및 거부

제8조 개인정보를 자동으로 수집하는 장치의 설치· 운영 및 거부

1. 쿠키의 사용 목적 : 이용자의 접속빈도나 방문시간 등을 파악하여 이용자에게 보다 편리한 서비스를 제공하기 위해 사용됩니다.

2. 쿠키의 설치·운영 및 거부: 브라우저 옵션 설정을 통해 쿠키 허용 및 차단 등의 설정을 할 수 있습니다.

① Internet Explorer : 웹브라우저 우측 상단의 도구 메뉴 > 인터넷 옵션 > 개인정보 > 설정 > 고급

② Edge: 웹브라우저 우측 상단의 설정 메뉴 > 쿠키 및 사이트 권한 > 쿠키 및 사이트 데이터 관리 및 삭제

③ Chrome: 웹브라우저 우측 상단의 설정 메뉴 > 개인정보 및 보안 > 쿠키 및 기타 사이트 데이터

제9조 개인정보보호 책임자

제9조 개인정보보호 책임자

1. ISRC는 개인정보 처리에 관한 업무를 총괄해서 책임지고, 개인정보 처리와 관련한 정보주체의 불만처리 및 피해구제 등을 위하여 아래와 같이 개인정보 보호책임자를 지정하고 있습니다.

- 구분

- 성명

- 담당부서

- 연락처

- 이메일

- 개인정보 보호책임자

- 서창수

- 행정실

- 02-880-5441

- csseo@snu.ac.kr

- 개인정보보호 담당부서

- 이은경

- 장비운영실

- 02-880-5449

- eklovelee@snu.ac.kr

2. 정보주체는 ISRC의 서비스를 이용하시면서 발생한 모든 개인정보보호 관련 문의, 불만처리, 피해구제 등에 관한 사항을 개인정보 보호책임자 및 담당부서로 문의할 수 있습니다. ISRC는 정보주체의 문의에 대해 지체없이 답변 및 처리해드릴 것입니다.

제10조 개인정보 열람청구

제10조 개인정보 열람청구

1. 정보주체는 「개인정보 보호법」 제35조에 따른 개인정보의 열람 청구를 아래의 부서에 할 수 있습니다. ISRC는 정보주체의 개인정보 열람청구가 신속하게 처리되도록 노력하겠습니다.

- 구분

- 성명

- 담당부서

- 연락처

- 이메일

- 개인정보보호 담당부서

- 이은경

- 장비운영실

- 02-880-5449

- eklovelee@snu.ac.kr

2. 정보주체께서는 제1항의 열람청구 접수·처리부서 이외에, 개인정보보호위원회 개인정보보호 포털을 통해서도 개인정보 열람청구를 하실 수 있습니다.

청구절차: 개인정보보호위원회 개인정보보호 포털(www.privacy.go.kr) → 민원마당 → 개인정보 열람등 요구

제11조 권익침해 구제방법

제11조 권익침해 구제방법

1. 정보주체는 개인정보침해로 인한 구제를 받기 위하여 개인정보분쟁조정위원회, 한국인터넷진흥원 개인정보침해신고센터 등에 분쟁해결이나 상담 등을 신청할 수 있습니다. 이 밖에 기타 개인정보침해의 신고, 상담에 대하여는 아래의 기관에 문의하시기 바랍니다.

① 개인정보분쟁조정위원회: (국번없이) 1833-6972 (www.kopico.go.kr)

② 개인정보침해신고센터: (국번없이) 118 (privacy.kisa.or.kr)

③ 대검찰청: (국번없이) 1301 (www.spo.go.kr)

④ 경찰청: (국번없이) 182 (ecrm.cyber.go.kr/minwon/main)

2. 「개인정보 보호법」 제35조(개인정보의 열람), 제36조(개인정보의 정정·삭제), 제37조(개인정보의 처리정지 등)의 규정에 의한 요구에 대 하여 공공기관의 장이 행한 처분 또는 부작위로 인하여 권리 또는 이익의 침해를 받은 자는 행정심판법이 정하는 바에 따라 행정심판을 청구할 수 있습니다.

① 중앙행정심판위원회 : (국번없이) 110 (www.simpan.go.kr)

제12조 개인정보 처리방침 변경

제12조 개인정보 처리방침 변경

1. 이 개인정보처리방침은 2024년 5월 1일부터 시행됩니다. 시행일로부터 적용되며, 법령 및 방침에 따른 변경내용의 추가, 삭제 및 정정이 있는 경우에는 변경사항의 시행 7일 전부터 공지사항을 통하여 고지할 것입니다.